### 演算子

#### ●演算子

ゲートレベル②

本科目では扱わない

簡単な例

高度な例

論理式記述-組み合わせ回路 機能記述-組み合わせ回路----機能記述-レジスタ 複合回路

RTL

### (例)組み合わせ回路の機能記述その1-A

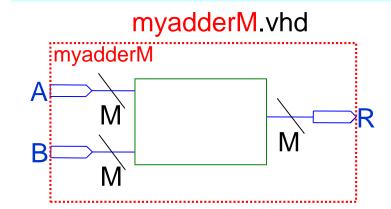

●算術演算子のみを用いた組み合わせ回路の機能記述

#### エンティティ名.vhd

### キャリー入出力なしMビット加算回路

#### ジェネリック宣言の記述

```

generic(M:integer:=4);

```

#### 入出力ポートの記述

```

port(

A : in std_logic_vector(M-1 downto 0);

B : in std_logic_vector(M-1 downto 0);

R : out std_logic_vector(M-1 downto 0)

);

```

#### 回路機能の記述

$$R \ll A + B;$$

#### 【注】

本科目で用いている<u>パッケージ</u>により 算術演算子に対する、2つの被演算子の ビット長は異なっていてもよい。

### (例)組み合わせ回路の機能記述その1-B

●連接演算子のみを用いた組み合わせ回路の機能記述

### ジェネリック宣言の記述

```

generic(M:integer:=4);

```

### 入出力ポートの記述

```

port(

A : in std_logic_vector(M-1 downto 0);

X : out std_logic_vector(M-1 downto 0)

);

```

### 回路機能の記述

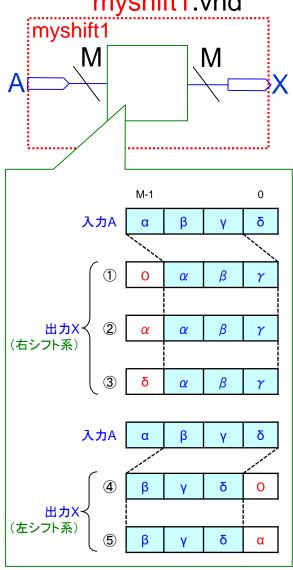

- 1 X<= '0' &A (M-1 downto 1);

- 論理右シフト

- $2 \times (M-1) &A (M-1)$

- 算術右シフト

- $3 \mid X \le A(0) \& A(M-1 \text{ downto } 1);$

- 右ローテート

- 4 X<=A (M-2 downto 0) &'0';

- 左シフト

- 5 X<=A (M-2 downto 0) &A (M-1);

左ローテート

#### 【注】連接演算子の解説 HW-5\_VHDL-01.pdf p.7 も参考に

# 1ビットシフト回路 myshift1.vhd

### (例)組み合わせ回路の機能記述その2

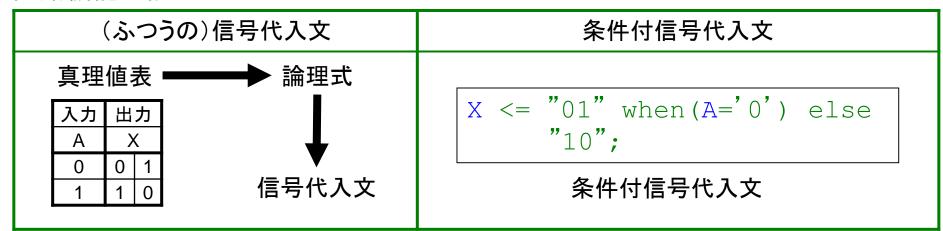

●条件付信号代入文を用いた組み合わせ回路の機能記述

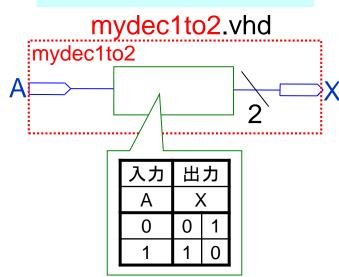

### 入出力ポートの記述

```

port(

A : in std_logic;

X : out std_logic_vector(1 downto 0)

);

```

### 1入力2出力デコーダ回路

### 回路機能の記述

### 条件付信号代入文

#### ●条件付信号代入文:

条件iに対応する、定数iまたは式iで決まる値を、信号に代入する。(i=1,…,n) 条件1~条件nのどれをも満たさない場合は、

定数Eまたは式Eで決まる値を、信号に代入する。

#### 書式

信号名 <= 定数1または<u>式</u>1 when(<u>条件</u>1) else 定数2または<u>式</u>2 when(<u>条件</u>2) else : 定数Nまたは<u>式</u>n when(<u>条件</u>n) else 定数Eまたは<u>式</u>E;

- ▶信号名(左辺とは別の)

- ▶<u>演算</u>式

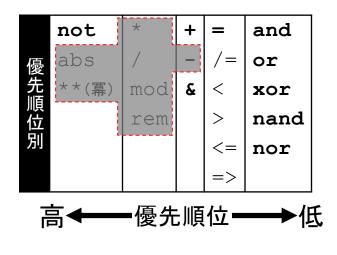

#### ●演算子

関係演算子を除く

|    | not   | *   | + | =     | and  |

|----|-------|-----|---|-------|------|

| 優  | abs   | /   | _ | /=    | or   |

| 先順 | **(冪) | mod | & | <     | xor  |

| 位  |       | rem |   | >     | nand |

| 別  |       |     |   | <=[*] | nor  |

|    |       |     |   | =>    |      |

優先順位--

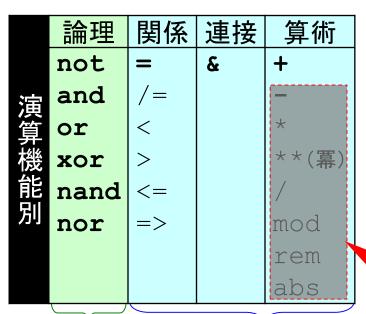

|        | 論理   | 関係        | 連接 | 算術    |

|--------|------|-----------|----|-------|

|        | not  | =         | &  | +     |

| · —    | and  | /=        |    | _     |

| )<br>算 | or   | <         |    | *     |

| 機      | xor  | >         |    | **(冪) |

| 能別     | nand | <=<br>[*) |    | /     |

|        | nor  | =>        |    | mod   |

|        |      | 1         |    | rem   |

|        |      |           |    | abs   |

| 【※】信号代入の記号ではない |       |         |   |  |  |  |  |

|----------------|-------|---------|---|--|--|--|--|

|                | —     |         | İ |  |  |  |  |

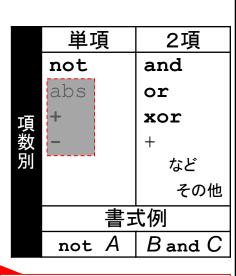

|                | 単項    | 2項      |   |  |  |  |  |

|                | not   | and     |   |  |  |  |  |

|                | abs   | or      |   |  |  |  |  |

| 項              | +     | xor     |   |  |  |  |  |

| 数              | _     | +       |   |  |  |  |  |

| 別              |       | など      |   |  |  |  |  |

|                |       | その他     |   |  |  |  |  |

|                | 書式例   |         |   |  |  |  |  |

|                | not A | B and C |   |  |  |  |  |

### ■必須課題■

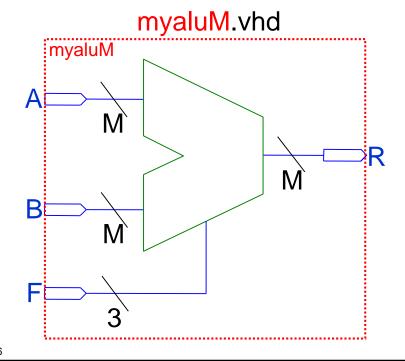

■プロジェクト「myaluM」 下の表は、MビットALUの動作表である。 これについて、条件付信号代入文を用いて回路を設計せよ。

### なお、

- Mはジェネリック宣言で指定すること。

- ・算術加算の記述には、算術演算子「+」を使用すること。

| 入力 |     | J | 出力                  |  |  |  |  |

|----|-----|---|---------------------|--|--|--|--|

| F  |     |   | R                   |  |  |  |  |

| 0  | 0   | 0 | AとBの算術加算値(キャリー出力なし) |  |  |  |  |

| 0  | 0   | 1 | AとBの論理積の値           |  |  |  |  |

| 0  | 1   | 0 | AとBの論理和の値           |  |  |  |  |

| 0  | 1   | 1 | AとBの排他的論理和の値        |  |  |  |  |

| そ  | その他 |   | Aの値                 |  |  |  |  |

### ▲追加課題▲

▲プロジェクト「mydec2to4」 下の表は、2入力4出力デコーダの真理値表である。 これについて、条件付信号代入文を用いて回路を設計せよ。

| 入 | 力 | 出力      |   |   |   |  |  |

|---|---|---------|---|---|---|--|--|

| A | 4 | X       |   |   |   |  |  |

| 0 | 0 | 0 0 0 1 |   |   |   |  |  |

| 0 | 1 | 0       | 0 | 1 | 0 |  |  |

| 1 | 0 | 0       | 1 | 0 | 0 |  |  |

| 1 | 1 | 1       | 0 | 0 | 0 |  |  |

### ▲追加課題▲

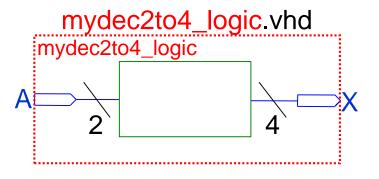

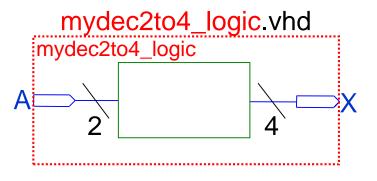

▲プロジェクト「mydec2to4\_logic」 下の表は、2入力4出力デコーダの真理値表である。 これについて、「真理値表→論理式→信号代入文」の手順で回路を設計せよ。

| 入   | 力 | 出力 |   |   |   |  |  |

|-----|---|----|---|---|---|--|--|

| L A | 4 | Х  |   |   |   |  |  |

| 0   | 0 | 0  | 0 | 0 | 1 |  |  |

| 0   | 1 | 0  | 0 | 1 | 0 |  |  |

| 1   | 0 | 0  | 1 | 0 | 0 |  |  |

| 1   | 1 | 1  | 0 | 0 | 0 |  |  |

## これまでの例の整理

| Top-Level Entity名 | スライド    | 論理回路種別 | 代入文                   | 演算子   | 内部信号 | generic宣言 |                                                     | モジュール化<br>デザイン |

|-------------------|---------|--------|-----------------------|-------|------|-----------|-----------------------------------------------------|----------------|

| mynand2           | VHDL-01 | 組み合わせ  | 信号代入                  | 論理    | _    |           | _                                                   | _              |

| myor3             | VHDL-02 | 組み合わせ  | 信号代入                  | 論理    | 0    |           | _                                                   | _              |

| mynand2xM         | VHDL-02 | 組み合わせ  | 信号代入                  | 論理    | _    | 0         | 値渡しなし                                               | _              |

| mynand2_cmp_inext | VHDL-02 | 組み合わせ  | 信号代入<br>(下位Level)     | 論理    | -    |           | _                                                   | 〇(その1)         |

| mynand2xM_cmp_or3 | VHDL-02 | 組み合わせ  | 信号代入<br>(Top/下位Level) | 論理    | 0    | 0         | 値渡しあり ・Top-Level (signal宣言文) ・下位Level (generic map) | ○(その2)         |

| mynand2_cmp_fg    | VHDL-02 | 組み合わせ  | 信号代入<br>(下位Level)     | 論理    | _    | 0         | 値渡しあり ・Top-Level (for-generate文)                    | ○(その3)         |

| myadderM          | VHDL-03 | 組み合わせ  | 信号代入                  | 算術(+) | _    |           | <del>-</del>                                        | _              |

| myshift1          | VHDL-03 | 組み合わせ  | 信号代入                  | 連接(&) | _    |           | <del>_</del>                                        | _              |

| mydec1to2         | VHDL-03 | 組み合わせ  | 条件付信号代入               | 関係    | _    |           | <del>_</del>                                        | _              |

バリエーション バリエーション なし

で学習

がやや増えた

先のステップ 次のステップ でさらに学習

さまざまなバリエーション で学習済

適宜応用する