## カウンタの設計 ~RTLでの機能図~

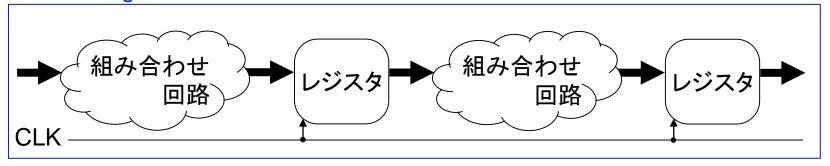

## RTL(Register Transfer Level:レジスタ転送レベル)での一般的回路機能図

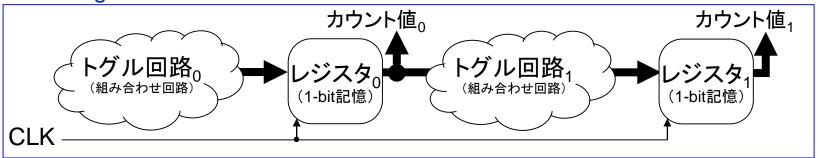

## RTL(Register Transfer Level:レジスタ転送レベル)でのカウンタの機能図その1

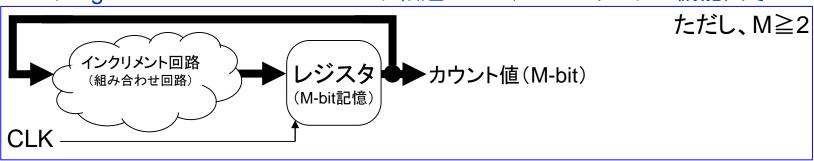

## RTL(Register Transfer Level:レジスタ転送レベル)でのカウンタの機能図その2

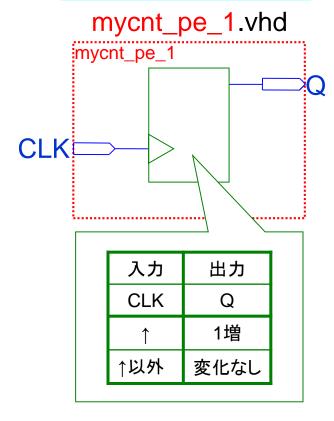

## (例)カウンタの機能記述① 基本カウンタ

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- •付加機能

基本カウンタ

- ・ポジティブエッジトリガ

- ・1-bitカウント

- → ・付加機能なし のカウンタ

#### 入出カポートの記述

```

port(

CLK : in std_logic;

Q : out std_logic

);

```

#### 各種宣言の記述

```

signal Y : std logic;

```

### 回路機能の記述

```

process(CLK)

begin

if(CLK'event and CLK='1')then

Y <= not Y;

end if;

end process;

Q <= Y;</pre>

```

【注】エンティティ名の「\_pe」はポジティブエッジトリガを、「\_1」は1-bitカウントを意図している

2プロセス

## (例)カウンタの機能記述② 多ビットカウンタ

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- ・カウントビット数

- •付加機能

カウントビット数: M

- ・ポジティブエッジトリガ

- M-bitカウント

- → ・付加機能なし のカウンタ

```

ジェネリック宣言の記述

generic (M:integer:=4);

```

### 入出カポートの記述

```

port (

CLK: in std logic;

Q : out std logic vector (M-1 downto 0)

```

### 各種宣言の記述

```

signal Y: std logic vector (M-1 downto 0);

```

### 回路機能の記述

```

process (CLK)

begin

if (CLK'event and CLK='1') then

2プロセス

Y <= Y + '1';

end if;

end process;

\circ <= Y;

```

K. Ichijo, Hirosaki University p.3

mycnt\_pe\_M.vhd mycnt\_pe\_M CLK 入力 出力 CLK 1増 ↑以外 変化なし

## 【注】エンティティ名の 「 **M**」はM-bitカウントを意図している

## (例)カウンタの機能記述③ 1ビット→多ビット

### 1ビットカウンタ

## 多ビットカウンタ

## ジェネリック宣言の記述

```

generic(M:integer:=4);

```

### 入出力ポートの記述

```

port(

CLK : in std_logic;

Q : out std_logic

);

```

### 入出力ポートの記述

```

port(

CLK : in std_logic;

Q : out std_logic_vector(M-1 downto 0)

);

```

#### 回路機能の記述

```

process(CLK)

begin

if(CLK'event and CLK='1')then

Y <= not Y;

end if;

end process;

Q <= Y;</pre>

```

#### 回路機能の記述

```

process(CLK)

begin

if(CLK'event and CLK='1')then

Y <= Y + '1';

end if;

end process;

Q <= Y;</pre>

```

- ✓ 変更の容易性を鑑みて、カウントビット数をジェネリック宣言で用意し、 カウント値出力ポートをstd logic vector型に変更。

- ✓ 回路機能は、トグル動作では対応できないので、インクリメントに変更。

## (例)カウンタの機能記述④ 付加機能一覧

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- ·付加機能

14種類の付加機能

継むの作用と

- ・ポジティブエッジトリガ

- •M-bitカウント

- 付加機能?????

のカウンタ

×

複数の機能を同時に付加することもできる

|                            |                                     | 機能のための | 饿肥を                      | 機能の作用と                                     | 複数          |

|----------------------------|-------------------------------------|--------|--------------------------|--------------------------------------------|-------------|

| 付加機能                       | 機能の意味                               | 入力ポート名 | 有効にする                    | クロック信号                                     | する          |

|                            |                                     | の例     | 入力値                      | との関係                                       |             |

| Clear                      |                                     | ACLRN  | 0                        | クロック非同期                                    | [例1]        |

|                            | 出力 <sub>※</sub> を                   | SCLRN  | U                        | クロック同期                                     |             |

| (Reset)                    | 常に0にする。                             | ACLR   | 4                        | クロック非同期                                    |             |

| 機能                         |                                     | SCLR   | l                        | クロック同期                                     |             |

| Lood                       |                                     | ALDN   | 0                        | クロック非同期                                    |             |

| Load                       | 出力を<br>任意の値にする。                     | SLDN   | 0                        | クロック同期                                     |             |

| (Set)<br>機能                |                                     | ALD    | 4                        | クロック非同期                                    |             |

|                            |                                     | SLD    | l                        | クロック同期                                     | [例2]        |

| Clock Enable               | クロック入力を                             | CEN    | 0                        |                                            | [例3]        |

| 機能                         | 許可する。                               | CE     | 1                        |                                            |             |

| Output Control<br>機能       | 出力 <sub>※</sub> を<br>High Impedance | OCN    | 0                        |                                            |             |

|                            | にする。 <u>≫</u>                       | OC     | 1                        |                                            | <u>(例4)</u> |

| <b>U</b> p/ <b>D</b> own切替 | カウント増/減を                            | UND    | 0 <b>⇒U</b> ,1 <b>⇒D</b> |                                            |             |

| 機能                         | 切り替える。                              | UDN    | 1 <b>⇒U</b> ,0 <b>⇒D</b> | クロック同期・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 例5)         |

機能のための<br />

機能を

集合体で指定

出力の<u>全ビット</u>

多ビットカウントの場合、

[例1]~[例5]は

以降で具体的に例示する。

それ以外は、例を参 考に記述してみよ。

K. Ichijo, Hirosaki University p.5

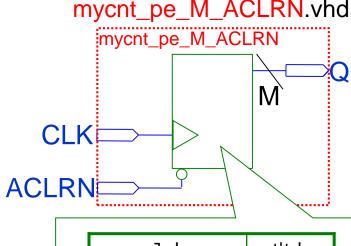

## (例)カウンタの機能記述⑤ 付加機能[例1]:ACLRN

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- •付加機能

clock Async. CLeaR Negative

ACLRN

付加機能一覧へ▲

- ・ポジティブエッジトリガ

- •M-bitカウント

- ·付加機能:ACLRN

のカウンタ

```

ジェネリック宣言の記述

```

generic(M:integer:=4);

#### 入出力ポートの記述

```

port(

CLK, ACLRN : in std_logic;

Q : out std_logic_vector(M-1 downto 0)

);

```

#### 各種宣言の記述

signal Y : std\_logic\_vector(M-1 downto 0);

#### 回路機能の記述

```

process (ACLRN, CLK)

begin

if (ACLRN='0') then

Y <= (others=>'0');

elsif(CLK'event and CLK='1') then

Y <= Y + '1';

end if;

end process;

Q <= Y;</pre>

```

| 入     | 出力  |      |  |

|-------|-----|------|--|

| ACLRN | CLK | Q    |  |

| 0     | _   | 0クリア |  |

| 1     | 1   | 1増   |  |

| ı     | ↑以外 | 変化なし |  |

【注】エンティティ名に付加機能の意を含めている

2プロセス

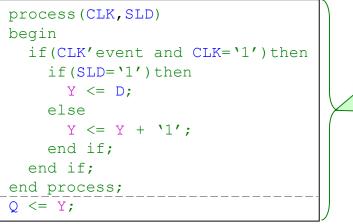

## (例)カウンタの機能記述⑥ 付加機能[例2]:SLD

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- •付加機能

```

clock Synchronous LoaD

SLD

```

付加機能一覧へ▲

- ・ポジティブエッジトリガ

- •M-bitカウント

- ·付加機能:SLD

- のカウンタ

```

ジェネリック宣言の記述 generic (M:integer:=4);

```

#### 入出力ポートの記述

```

port(

CLK, SLD : in std_logic;

D : in std_logic_vector(M-1 downto 0);

Q : out std_logic_vector(M-1 downto 0)

);

```

#### 各種宣言の記述

```

signal Y : std_logic_vector(M-1 downto 0);

```

#### 回路機能の記述

| mycnt_pe_N                            | <b>∄_SLD</b> .vhd |

|---------------------------------------|-------------------|

| mycnt_pe_M_                           | SLD               |

| D                                     |                   |

| M                                     | M                 |

| CLK                                   |                   |

|                                       |                   |

| SLD                                   |                   |

| · · · · · · · · · · · · · · · · · · · |                   |

|                                       |                   |

|       | 出力  |   |      |  |  |

|-------|-----|---|------|--|--|

| CLK   | SLD | D | Q    |  |  |

| •     | 1   | - | D    |  |  |

|       | 0   | - | 1増   |  |  |

| ↑以外 - |     | - | 変化なし |  |  |

【注】エンティティ名に付加機能の意を含めている

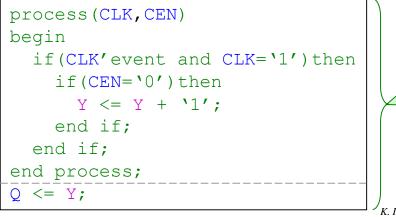

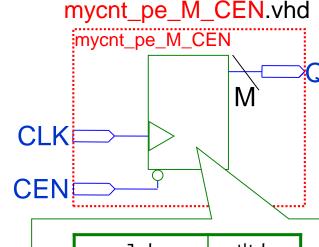

## (例)カウンタの機能記述⑦ 付加機能[例3]:CEN

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- •付加機能

- •追加出力

```

Clock Enable Negative

CEN

```

付加機能一覧へ▲

・ポジティブエッジトリガ

•M-bitカウント

·付加機能:CEN

・追加出力なし

のカウンタ

```

ジェネリック宣言の記述

```

generic(M:integer:=4);

#### 入出カポートの記述

```

port (

CLK, CEN: in std logic;

Q : out std logic vector (M-1 downto 0)

```

#### 各種官言の記述

signal Y : std logic vector(M-1 downto 0);

#### 回路機能の記述

| 入   | 出力  |      |  |  |

|-----|-----|------|--|--|

| CLK | CEN | Q    |  |  |

| •   | 0   | 1増   |  |  |

|     | 1   | 赤ルか  |  |  |

| ↑以外 | _   | 変化なし |  |  |

【注】エンティティ名に付加機能の意を含めている

K. Ichijo, Hirosaki University p.8

2プロセス

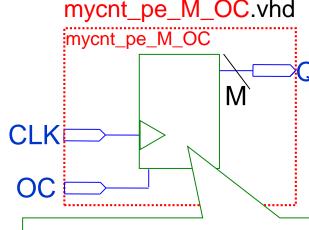

## (例)カウンタの機能記述® 付加機能[例4]:OC

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- •付加機能

```

Output Control

OC

```

付加機能一覧へ▲

- ・ポジティブエッジトリガ

- •M-bitカウント

- → ·付加機能:OC

- のカウンタ

```

ジェネリック宣言の記述

```

```

generic(M:integer:=4);

```

### 入出力ポートの記述

```

port(

CLK, OC : in std_logic;

Q : out std_logic_vector(M-1 downto 0)

);

```

### 各種宣言の記述

```

signal Y : std logic vector(M-1 downto 0);

```

### <u>回路機能の記述</u>

```

process(CLK)

begin

if(CLK'event and CLK='1')then

Y <= Y + '1';

end if;

end process;

Q <= (others=>'Z') when(OC='1') else Y;

```

| 入力  | J  | 出力             |  |  |

|-----|----|----------------|--|--|

| CLK | ОС | Q              |  |  |

| 1   |    | 1増             |  |  |

| ↑以外 | 0  | 変化なし           |  |  |

| -   | 1  | High Impedance |  |  |

【注】エンティティ名に付加機能の意を含めている

ロセス

## (例)カウンタの機能記述⑨ 付加機能[例5]:UDN

- ●カウンタの機能記述

- ・ポジティブ/ネガティブ エッジトリガ

- カウントビット数

- •付加機能

Up count/ Down count Neg.

付加機能一覧へ▲

- ・ポジティブエッジトリガ

- •M-bitカウント

- ·付加機能:UDN

のカウンタ

```

ジェネリック宣言の記述

```

generic(M:integer:=4);

#### 入出カポートの記述

```

port(

CLK, UDN : in std_logic;

Q : out std_logic_vector(M-1 downto 0)

);

```

#### 各種宣言の記述

```

signal Y : std logic vector(M-1 downto 0);

```

#### 回路機能の記述

```

process(CLK,UDN)

begin

if(CLK'event and CLK='1')then

if(UDN='1')then

Y <= Y + '1';

else

Y <= Y + (M-1 downto 0=>'1');

end if;

end process;

Q <= Y;</pre>

```

2プロセス

mycnt\_pe\_M\_UDN.vhd

mycnt\_pe\_M\_UDN

CLK

UDN

| 入     |     | 出力   |  |  |

|-------|-----|------|--|--|

| CLK   | UDN | Q    |  |  |

| 1     | 1   | 1増   |  |  |

|       | 0   | 1減   |  |  |

| ↑以外 - |     | 変化なし |  |  |

【注】エンティティ名に付加機能の意を含めている

## ■必須課題■

以下のカウンタのプロジェクトについての設計をせよ。

■ mycnt\_pe\_M\_ACLR\_CE\_SLD

### なお、

- ✓\_peは、ポジティブエッジトリガの意味である。

- ✓ Mは、M-bitカウントの意味である。

- ✓Mはジェネリック宣言で指定できるようにすること。

- ✓ \_ACLR, \_CE, \_SLDは、 付加機能一覧の表の「機能のための入力ポート名の例」と同じとして考えよ。≫

## ▲追加課題▲

以下のカウンタのプロジェクトについての設計をせよ。

▲ mycnt\_pe\_M\_ACLR\_SCLR

### なお、

- ✓\_peは、ポジティブエッジトリガの意味である。

- ✓ Mは、M-bitカウントの意味である。

- ✓Mはジェネリック宣言で指定できるようにすること。

- ✓ \_ACLR, \_SCLRは、 付加機能一覧の表の「機能のための入力ポート名の例」と同じとして考えよ。≫

# これまでの例の整理

| Top-Level Entity名 | スライド    | 論理回路種別   | Process文     | 代入文                   | 演算子   | 内部信号 |   | generic宣言                                           | モジュール化<br>デザイン |

|-------------------|---------|----------|--------------|-----------------------|-------|------|---|-----------------------------------------------------|----------------|

| mynand2           | VHDL-01 | 組み合わせ    | _            | 信号代入                  | 論理    | _    |   | _                                                   | _              |

| myor3             | VHDL-02 | 組み合わせ    | _            | 信号代入                  | 論理    | 0    |   | _                                                   | _              |

| mynand2xM         | VHDL-02 | 組み合わせ    | _            | 信号代入                  | 論理    | _    | 0 | 値渡しなし                                               | _              |

| mynand2_cmp_inext | VHDL-02 | 組み合わせ    | _            | 信号代入<br>(下位Level)     | 論理    | 1    |   | -                                                   | 〇(その1)         |

| mynand2xM_cmp_or3 | VHDL-02 | 組み合わせ    | -            | 信号代入<br>(Top/下位Level) | 論理    | 0    | 0 | 値渡しあり ・Top-Level (signal宣言文) ・下位Level (generic map) | ○(その2)         |

| mynand2_cmp_fg    | VHDL-02 | 組み合わせ    | _            | 信号代入<br>(下位Level)     | 論理    | ı    | 0 | 値渡しあり<br>・Top-Level<br>(for-generate文)              | ○(その3)         |

| myadderM          | VHDL-03 | 組み合わせ    | _            | 信号代入                  | 算術(+) | _    |   | _                                                   | _              |

| myshift1          | VHDL-03 | 組み合わせ    | _            | 信号代入                  | 連接(&) | _    |   | _                                                   | _              |

| mydec1to2         | VHDL-03 | 組み合わせ    | _            | 条件付信号代入               | 関係    | _    |   | _                                                   | _              |

| myenc4to2         | VHDL-04 | 組み合わせ    | O(if)        | 信号代入                  | 関係    | 1    |   | _                                                   | _              |

| mydec1to2         | VHDL-04 | 組み合わせ    | O(case)      | 信号代入                  | なし    | 1    |   | _                                                   | _              |

| myandM            | VHDL-04 | 組み合わせ    | O (for-loop) | 変数代入                  | 論理    | 1    | 0 | 値渡しあり<br>(for-loop文)                                | _              |

| myreg_***         | VHDL-05 | 順序(記憶要素) | O(if)        | 信号代入<br>条件付信号代入       | 論理    | 0    | 0 | 値渡しあり<br>(signal宣言文、集合体)                            | _              |

| mycnt_***         | VHDL-06 | 順序       | O(if)        | 信号代入<br>条件付信号代入       | 算術(+) | 0    | 0 | 値渡しあり<br>(signal宣言文、集合体)                            | _              |

さまざまなバリエーションで学習済